Front Panel Deposit Operation

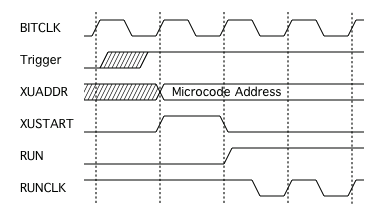

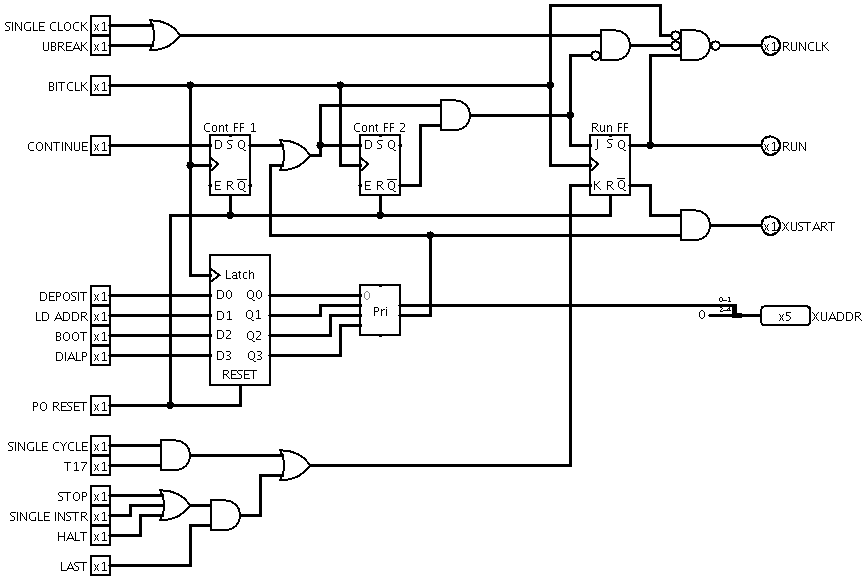

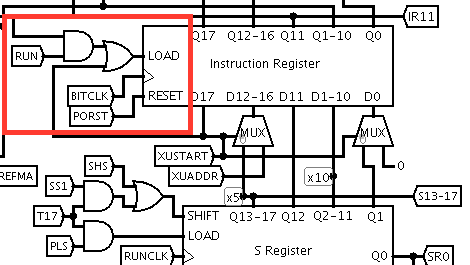

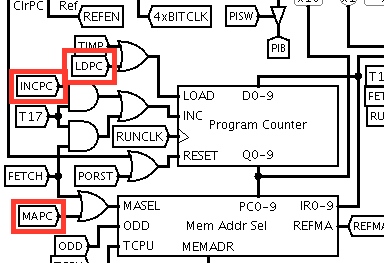

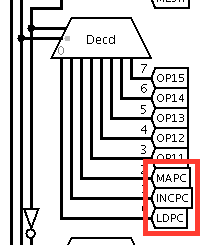

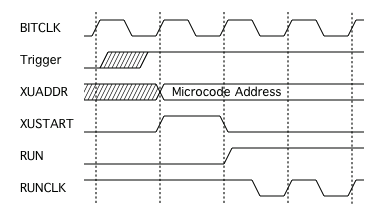

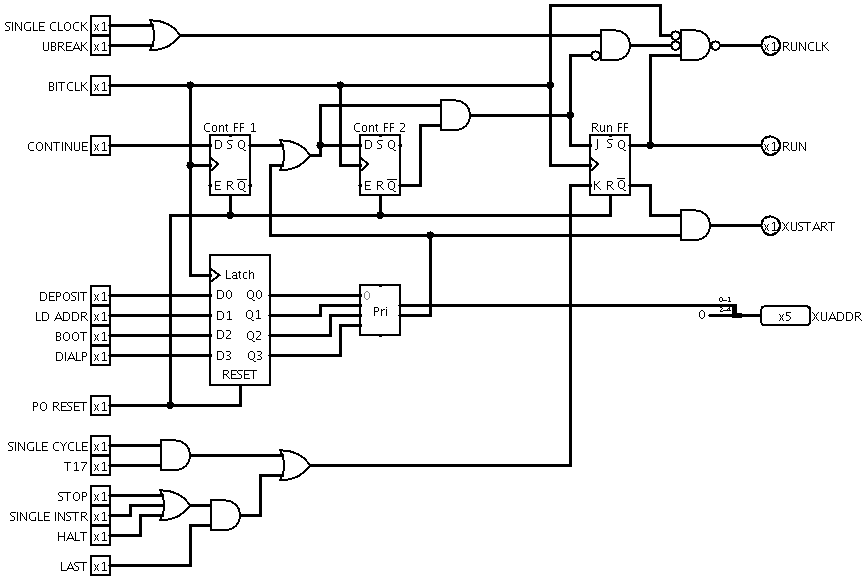

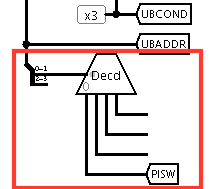

The Run Control subcircuit now has provision for initiating up to four

different non-instruction microcode sequences (NIMS). The inputs for

triggering these are first latched to synchronise them with BITCLK, and

then fed to a priority encoder which generates a microcode address. At

the same time, the Continue FF chain is activated, producing a

one-BITCLK pulse at XUSTART and then setting the Run FF.

NIMS Timing

Run Control

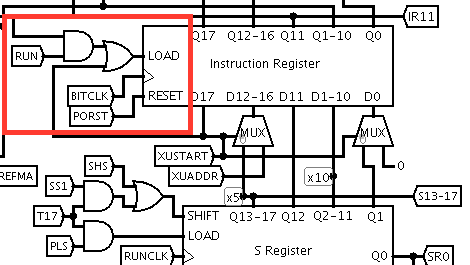

Instruction Register Loading

I found a problem with the logic for loading the NIMS entry point

address into the instruction register. It doesn't work if the

instruction register is clocked with RUNCLK, because the XUSTART pulse

occurs before RUNCLK is activated. So the instuction register is now

continuously clocked with BITCLK, and functions that should only occur

while the machine is running are gated with RUN.

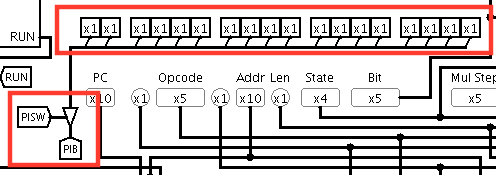

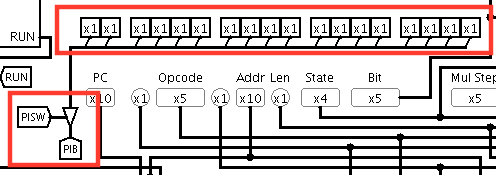

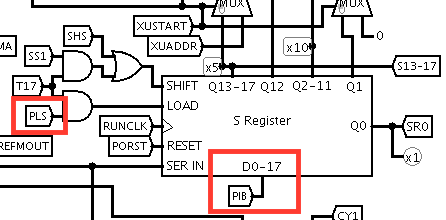

Input Switches and Parallel Input Bus

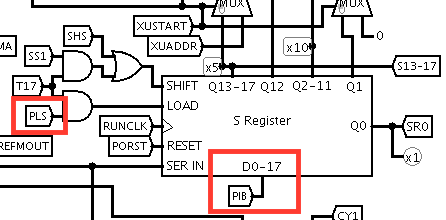

I added a set of switches for manual data entry1. These are gated onto a Parallel Input Bus (PIB) which connects to new parallel inputs on the S register.

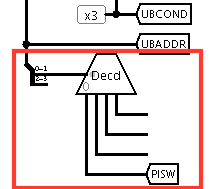

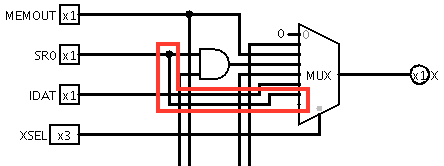

There is currently only one data source for the PIB, but there will be

others later. I needed a way of selecting the PIB source in the

microcode, but there are no more bits available, so I have re-used part

of the UBADDR field. This means I won't be able to perform a microcode

branch and use the PIB at the same time, but I don't think that will be

a problem.

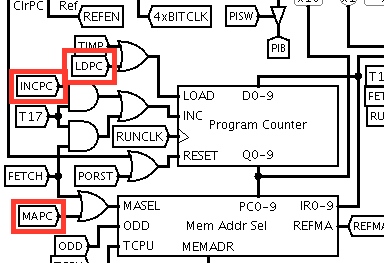

The function of the Deposit switch will be to write the value from the

input switches into memory at the address currently in the PC, and then

increment the PC. To do this, I need to be able to select the PC as the

source for the memory address, and increment the PC, independently of

other functions.

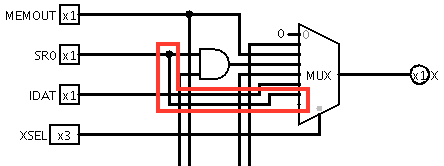

I also need to be able to select the serial output of the S register as an X source in the ALU input selector.

With these changes in place, the Deposit operation can be microcoded.

# XSEL values

XSR = 011 # S Register

# MISC values

PLS = 1110 # Parallel load S register

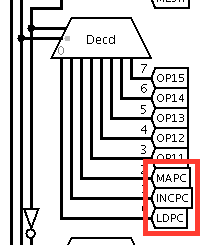

LDPC = 0001 # Load PC from IR

INCPC = 1001 # Increment PC

MAPC = 0101 # Memory address = PC

# Deposit

1 00000 0 0000 : - - -- --- - -- - - -- - - - - - - PLS - --- PISW -- # Load switches into S

1 00000 0 0001 : SHS - -- XSR - -- - WMEM -- - - - - - - MAPC - --- ---- # Write S to memory

1 00000 0 0010 : - - -- --- - -- - - -- - - - - - - INCPC - --- ---- # Increment PC

1 00000 0 0011 : - EOI -- --- - -- - - -- - - - - - - HALT - --- ---- # Stop

Footnotes

1. This is not quite historically

accurate. The EDSAC designers deliberately did not provide a way for

users to enter programs manually, because they didn't want people

taking up machine time debugging at the console. It did have a set of

"engineering switches" that were used for maintenance, but I don't know

exactly what they did or how they were used.